| КОМПЬЮТЕРЫ |   |

С момента появления первых компьютеров разработчики программ мечтали об аппаратуре, предназначенной для решения именно их задачи. Поэтому уже довольно давно появилась идея создания специальных интегральных схем, которые можно затачивать под эффективное выполнение конкретной задачи. Здесь можно выделить два пути развития:

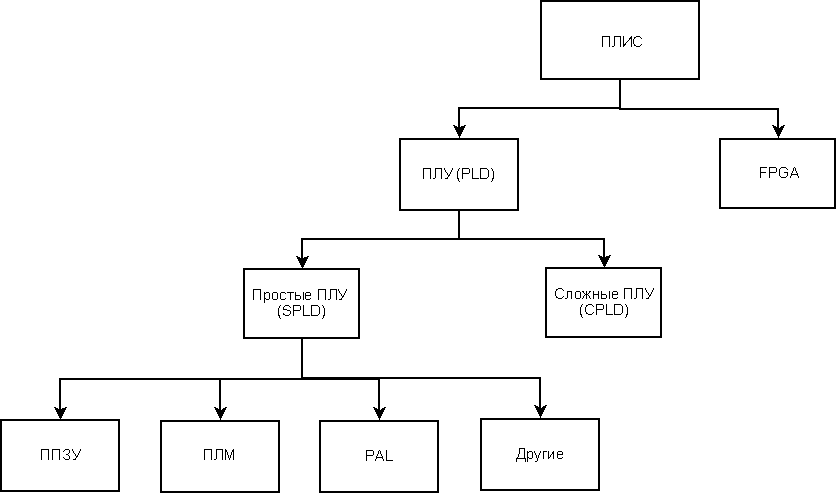

Со временем появлялось большое количество разнообразных микросхем с реконфигурируемой архитектурой (Рис. 1).

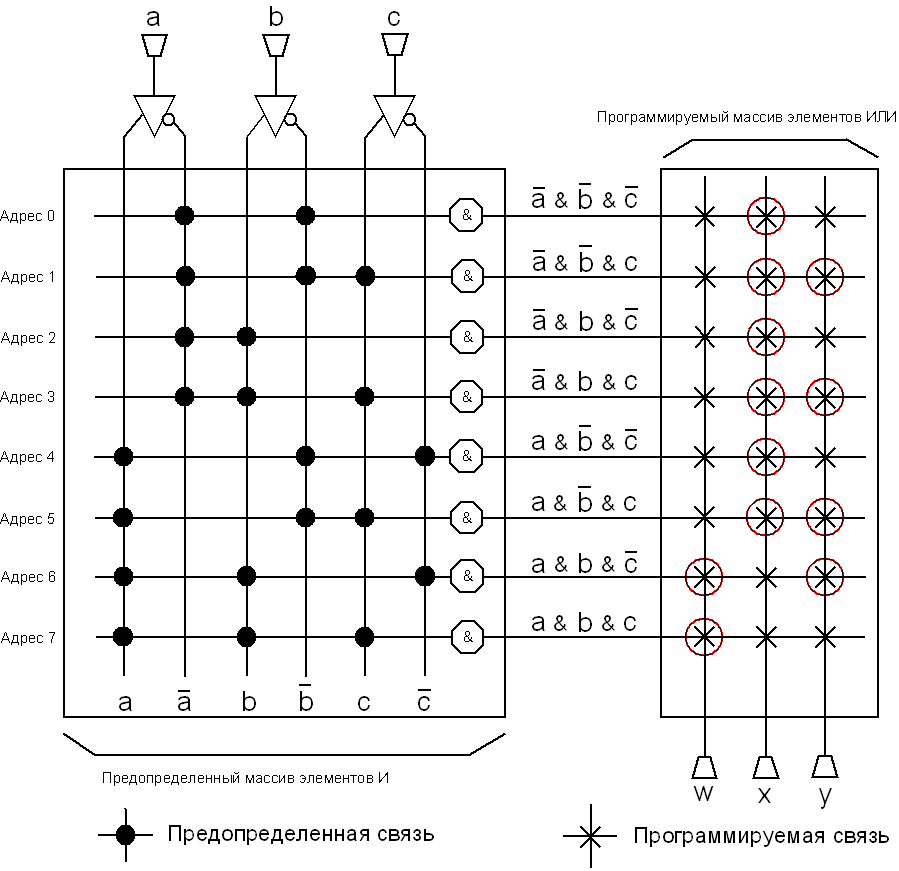

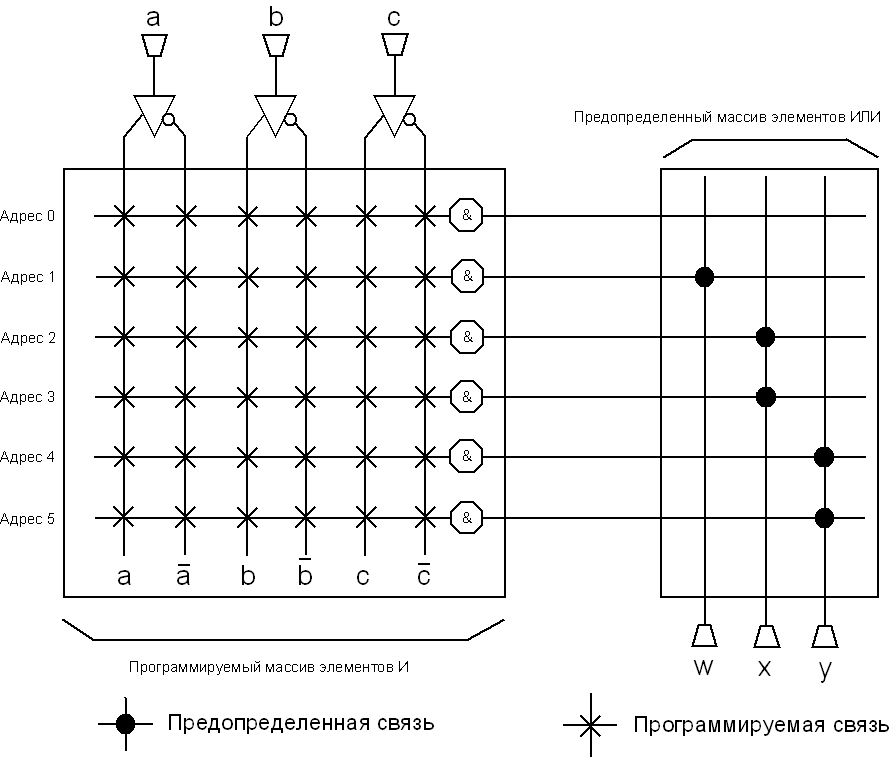

В течение довольно длительного времени на рынке существовали только PLD (Programmable Logic Device) устройства. В этот класс выделяются устройства, которые реализуют функции, необходимые для решения поставленных задач, в виде совершенной дизъюнктивной нормальной формы (совершенной ДНФ). Первыми в 1970 году появились ППЗУ-микросхемы, которые относятся как раз к классу PLD-устройств. Каждая схема имела фиксированный массив логических функций И, подсоединенный к программируемому набору логических функций ИЛИ. Для примера рассмотрим ППЗУ с 3 входами (a,b и с) и 3 выходами (w,x и y) (Рис. 2).

C помощью предопределенного массива И реализуются все возможные конъюнкции над входными переменными, которые затем могут быть произвольным образом объединены с помощью ИЛИ элементов. Таким образом, на выходе можно реализовать любую функцию от трех переменных в виде совершенной ДНФ. Например, если запрограммировать те элементы ИЛИ, которые обведены в красный кружок на рисунке 2, то на выходах получатся функции w=a&b; x=(a&b); y=(a&b)^c.

Изначально микросхемы ППЗУ предназначались для хранения программных инструкций и значений констант, т.е. для выполнения функций компьютерной памяти. Однако разработчики используют их также для реализации простых логических функций. В действительности ППЗУ микросхемы можно использовать для реализации любого логического блока, при условии, что он имеет небольшое количество входов. Это условие вытекает из того факта, что в ППЗУ микросхемах жестко определена матрица элементов И - в ней реализуются все возможные конъюнкции от входов, то есть число элементов И равно 2*2n, где n - число входов. Понятно, что при увеличении числа n размер массива растет очень быстро.

Следующими в 1975 году появились так называемые программируемые логические матрицы (ПЛМ). Они являются продолжением идеи ППЗУ микросхем - ПЛМ также состоят из И и ИЛИ массивов, однако в отличие от ППЗУ оба массива программируемы. Это обеспечивает большую гибкость таких микросхем, однако они никогда не были распространены по той причине, что для похождения через программируемые связи сигналам требуется намного больше времени, чем при прохождении через их предопределенные аналоги.

Для того чтобы решить проблему скорости, свойственную ПЛМ, в конце 1970-х появилось следующий класс устройств, называемый программируемый массив логики (PAL - Programmable Array Logic). Дальнейшим развитием идеи PAL-микросхем стало появление устройств GAL (Generic Array Logic) - более сложных разновидностей PAL с использованием КМОП-транзисторов. Здесь используется идея, ровно противоположная идее ППЗУ-микросхем - программируемый массив элементов И подключается к предопределенному массиву элементов ИЛИ (Рис. 3).

Это накладывает ограничение по функциональности, однако в таких устройствах требуются массивы значительно меньшего размера, нежели в ППЗУ микросхемах.

Логическим продолжением простых PLD стало появление так называемых сложных PLD, состоящих из нескольких блоков простых PLD (обычно в качестве простых PLD используются PAL-устройства), объединенных программируемой коммутационной матрицей. Помимо самих блоков PLD можно было также запрограммировать связи между ними с помощью данной коммутационной матрицы. Первые сложные PLD появились в конце 70-х - начале 80-х годов 20 века, однако основное развитие этого направления пришлось на 1984 год, когда компания Altera представила сложное PLD, основанное на сочетании КМОП- и СППЗУ-технологий.

В начале 80-х годов в среде цифровых специализированных микросхем образовался пробел между основными типами устройств. С одной стороны были PLD, которые можно программировать под каждую конкретную задачу и достаточно легко изготавливать, однако они не могут быть использованы для реализации сложных функций. С другой стороны есть ASIC, которые могут реализовывать чрезвычайно сложные функции, однако обладают жестко фиксированной архитектурой, при этом их долго и дорого изготавливать. Необходимо было промежуточное звено, и таким звеном стали FPGA (Field Programmable Gate Arrays)-устройства.

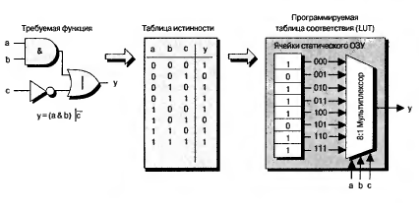

FPGA, как и PLD, являются программируемыми устройствами. Главным принципиальным отличием FPGA от PLD является то, что функции в FPGA реализуются не с помощью ДНФ, а помощью программируемых таблиц соответствия (LUT-таблиц). В этих таблицах значения функции задаются с помощью таблицы истинности, из которой необходимый результат выбирается с помощью мультиплексора (рис. 4):

Каждое FPGA-устройство состоит из программируемых логических блоков (Configurable Logic Blocks - CLB), которые связаны между собой соединениями, также программируемыми. Каждый такой блок предназначен для программирования некоторой функции или ее части, однако может быть использован для других целей, например, в качестве памяти.

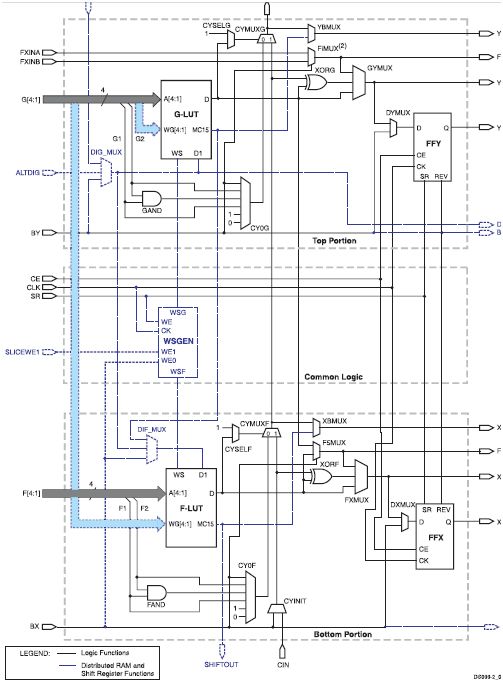

В первых FPGA-устройствах, разработанных в середине 80-х годов, логический блок был устроен очень просто и содержал одну 3-входовую LUT-таблицу, один триггер и небольшое количество вспомогательных элементов. Современные FPGA-устройства устроены гораздо сложнее: каждый CLB-блок состоит из 1-4 "срезов" (slice), каждый из которых содержит несколько LUT-таблиц (обычно 6-входовых), несколько триггеров и большого числа служебных элементов. Вот пример современного "среза":

Поскольку PLD-устройства не могут реализовывать сложные функции, они продолжают использоваться для реализации простых функций в портативных устройствах и коммуникациях, в то время как FPGA-устройства, начиная от размера в 1000 вентилей (первая FPGA, разработанная в 1985 году), на данный момент превысили отметку в 10 миллионов вентилей (семейство Virtex-6). Они активно развиваются и уже вытесняют ASIC-микросхемы, позволяя реализовывать самые различные чрезвычайно сложные функции, при этом не теряя возможности перепрограммирования.

© Лаборатория Параллельных информационных технологий НИВЦ МГУ